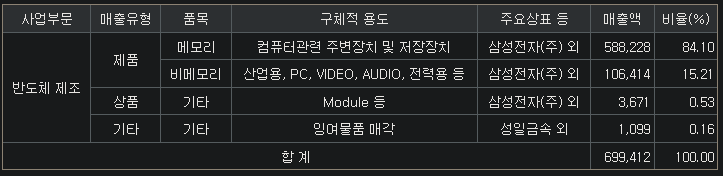

SFA반도체 사업

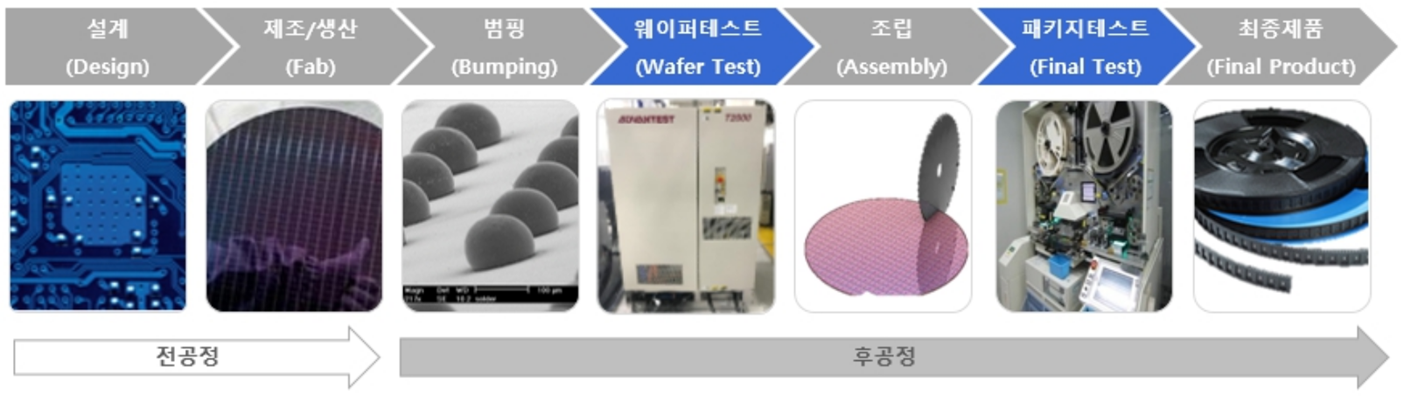

· 반도체 조립(Assembly) : Bumping, WLCSP(FO-WLP), Lead Frame, Storage(SSD, Micro SD Card)

· 반도체 테스트(Test) : Wafer Probe Test, Final Test

기회

· 서버투자 > DDR5 수요증가 > DDR5, DDR4에 비해 테스트시간 증가 > ASP 20~30% 상승예상

·

리스크

· 반도체제조사 모바일향 후공정 내재화 > 수주 감소 가능성

·

업데이트 :

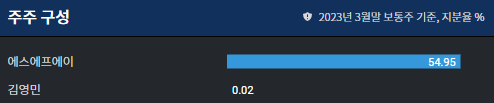

주주구성(23.3월 기준) :

SFA반도체

SFA반도체는 OSAT(Outsourced Semiconductor Assembly & Test)업체인데요. Bumping-Wafer Probe Test- Assembly-Final Test를 모두하고 있어요. Bumping은 기존에 칩을 기판에 연결할 때 사용하던 와이어본딩(Wire Bonding)방식을 대체하는 소재이구요(FCBGA or FCCSP). Wafer Probe Test는 전공정이 끝난 다이(Die)에 EDS(Electrical Die Sorting)공정테스트를 하는 것입니다. Assembly는 범핑된 칩을 기판에 연결 or 기판없이 WLCSP(Wafer Level Chip Scale Package)로 옷을 입히는 것을 의미해요. 반도체칩이 옷까지 입었다면 마지막으로 전기적 테스트, 고온/저온 테스트를 진행하는데 이를 Final Test라고 합니다. SFA반도체는 주요고객사가 삼성전자, SK하이닉스인 만큼 메모리향이 주력이며 점차 비메모리 OSAT서비스도 진출하고 있습니다.

반도체 조립(Assembly) : Bumping, WLCSP(FO-WLP, Fan-Out Wafer Level Package),

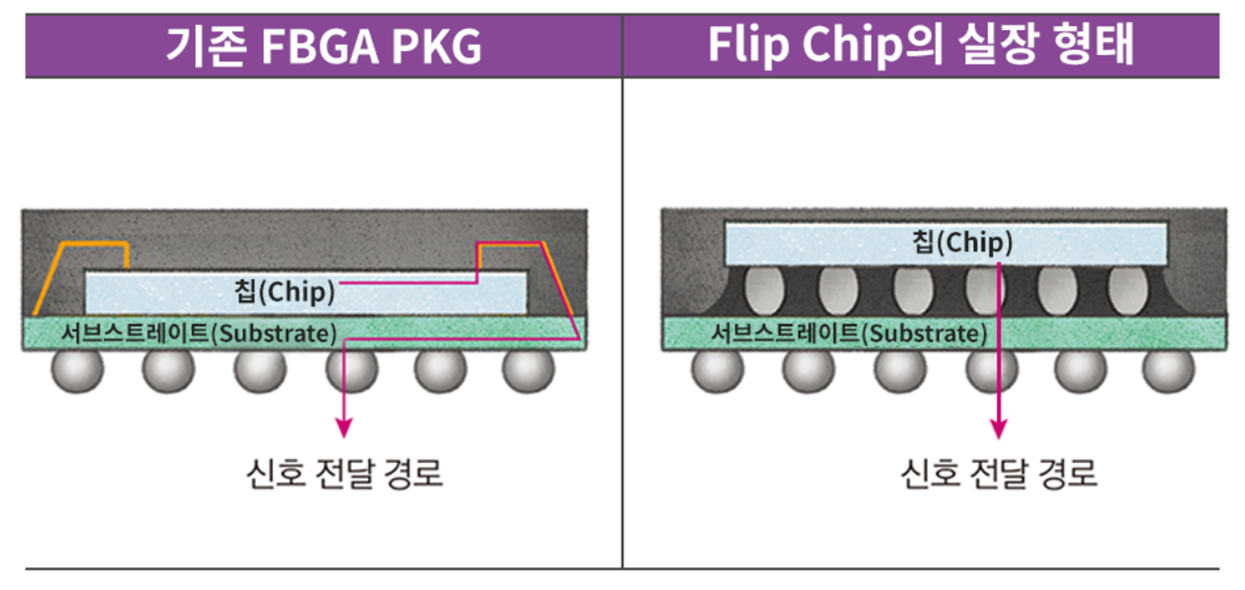

SFA반도체는 후공정업체로 반도체칩을 패키징을 하는데요. 패키징이라고 하면, 전공정에서 만든 웨이퍼 위 칩들에게 옷을 입혀주고(Substrate와 연결) 외부와 전기적 신호를 위해 기판(PCB)과 접촉시키는 것을 말해요. 특히, 예전에는 반도체칩을 와이어본딩(Wire Bonding) 방식으로 기판에 연결했다면, 요즘에는 Bumping으로 연결하여 더 빠른 신호, 강력한 신호들을 가능케하고 있어요.

심지어, 최근에는 기판(Substrate) 마저도 신호를 느리게 하고 패키지 크기를 축소하는데 방해가 된다고 해서 기판없는 패키징기술이 각광을 받고 있어요. 이를 WLCSP라고 부르는데요. Wafer Level Chip Scale Package의 약자입니다. 즉, 웨이퍼에서(Wafer Level) 바로 칩크기(Chip Scale)의 패키징을 한다는 것이에요. 기판도 없어지니 더 빠르고 얇은 반도체가 완성이 될 수 있겠죠. 이 외에도 Advanced Package기술로 Cu Pillar, Fan-in/out WLCSP, RDL, UBM 등이 있는데요. 경쟁사인 '하나마이크론, 후공정업계 1위'를 참고하면 이해하기 쉬울 거에요.

반도체 테스트(Test) : Memeory Test, Logice Test

반도체는 전공정이 끝난후 진행하는 Wafer Test와 후공정이 끝난 후 하는 Final Test 두 가지로 나뉘는데요. SFA반도체는 둘 다 테스트를 할 수 있어요. Wafer Test는 아직 패키징 전이기 때문에 Wafer가 알몸상태인데요. 이때, 프로브(Probe)를 갖다대서 EDS테스트(Electrical Die Sorting)를 해요. 전기적 테스트를 하는 것이죠. 아직, 'EDS공정, 단 번에 이해'를 안본 독자들은 꼭 보고오길 추천해요. Final Test 때는 반도체칩이 패키징이 완료된 이후겠죠? 패키징을 하는 과정에서 반도체칩이 전기적으로 아직 잘 살아있는지를 테스트합니다. 결국, 테스트를 하는 이유는 양품과 불량품을 가려내기 위함이고 이는 곧 반도체 수율과 직결되기 때문에 굉장히 중요한 작업이라 할 수 있어요.

연구실적으로 보는 SFA반도체의 현 주소 :

개인적으로 SFA반도체의 연구실적과 연구계획을 보면 동사의 현 상황과 미래 비전이 보인다고 생각을 하는데요. 같이 몇 개만 살펴볼까요.

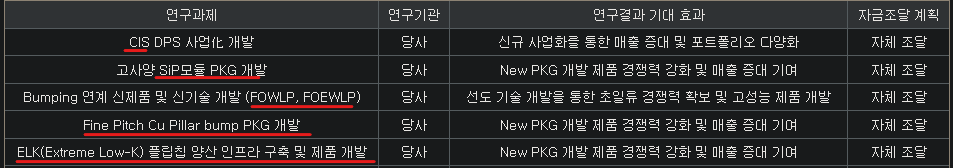

SFA반도체의 R&D를 간단하게만 설명드릴게요. 아래표는 동사의 연구계획인데요. CIS는 CMOS Image Sensor의 약자로 시스템반도체 패키지를 말하는 것 같아요. 동사의 주력은 메모리이기 때문에 사업다각화를 위해 본격적으로 비메모리향 OSAT투자를 하는 것 같아요. 바로 아래 SiP도 마찬가지로 비메모리에 속합니다. System in Package이죠. SiP란 CPU와 메모리가 하나의 패키지에 같이 있다고 생각하면 됩니다.

그 다음 R&D는 FOWLP인데요. Fan-Out Wafer Level Package의 약자에요. WLP는 기판(Substrate)없이 패키징을 한다는 것입니다. 즉, 웨이퍼상태에서 바로 패키징하는 것이죠. 이때, 칩을 잘라서 따로 패키징을 하는데, 이를 Fan-Out WLP라고 불러요. 자세한건 하나마이크론편을 참고해주세요. WLP의 가장 큰 문제는 패키징이 워낙 미세화되다 보니 솔더볼(Solder Ball)들이 제자리에 있기 힘들고 버티기도 힘들어요. 그래서, 전도성 금속인 구리를 이용하여 기둥을 세워서 버팀목이 되주는데요. 이를 Cu Pillar라고 부릅니다. 마지막으로, Low-k 플리칩관련 PKG인데요. High-k가 높은 유전율을 갖는다면(보통 4이상), Low-k는 낮은 유전율을 갖죠. 낮은 유전율 때문에 저항이 덜 생기는데, HBM(High Bandwidth Memory)같은 최근 AI반도체용 메모리칩에 적층용으로 사용되고 있어요. 방해를 안하니깐요(낮은 유전율).

SFA반도체에 대한 지속적인 업데이트는 맨 위 상단을 참고하면 유익합니다 :)

'반도체_후공정장비' 카테고리의 다른 글

| 미래산업, 테스트 핸들러 찾고계셨나요? (쉽게설명!) (0) | 2023.10.11 |

|---|---|

| 시그네틱스, 다른 OSAT업체보다는 늦어요. 근데, 사기에는 편해요(쉽게설명!) (0) | 2023.08.23 |

| 하나마이크론, 후공정 조립을 담당하는 1위업체 (쉽게설명!) (0) | 2023.08.21 |

| 두산테스나, OSAT업체를 찾는다면 반드시 봐야할 업체(쉽게설명!) (0) | 2023.08.18 |

| 테크윙, 마이크론이 가면 Handler도 간다! (쉽게설명) (0) | 2023.08.14 |