우선, 트랜지스터(Transistor)가 뭔지 알아볼까요 : 0과 1인 디지털정보 -> 전기신호

지금 여러분의 눈에는 제 글자가 하나하나 자세히 보이겠죠. 전혀 0과 1의 숫자로 보이지 않습니다. 다만, 컴퓨터 입장에서 생각해보죠. 한국어, 영어, 중국어로 모라고 하는데, 도저히 알아들을 수 없어요. 딱 한 가지 알아들을 수 있는 것은 말을 했는지 안했는지의 여부죠. 했으면 전기신호를 보내서 1. 안했으면 0으로 인식을 하게됩니다. 이때, 1과 0이 몇 번 들어오고 순서는 어떻게 들어오는지에 따라서 사람이 컴퓨터에게 특정 문자와 숫자를 알려줍니다. 예를 들면, "5번 신호를 보낼텐데, 마지막에만 전기신호 보내면 'A'로 하자" 이런식이죠. 그래서, 00001이 A를 가리키는 겁니다. 반대로, 5번 신호 중 4번째에 보내면 B로되는거죠( B : 00010).

한 마디로, 트랜지스터가 없다면 디지털정보 -> 전기신호로 바꿔주는 것이 되지않기 때문에, 전혀 컴퓨터와 소통을 할 수 없게됩니다. Transistor의 어원을 보면 trans(transfer : 전송하다) + istor(Varistor : 저항소자) 입니다. 말 그대로, 반응(저항)을 하면 1을 보내고 안하면 안보내고 하는 식인 것이죠. 이러한 트랜지스터의 중요성은 반도체 직접 생산하는 파운드리업체에게는 트랜지스터를 실리콘(Si)으로 이루어진 웨이퍼위에 가능한 많이 얹는게 유리하겠죠. 결국, 반도체의 역사는 트랜지스터를 더 작고 빠르게, 얼마나 저전력으로 고성능을 낼 수 있는지로 봐도 전혀 문제가 없습니다.

면적의 유무가 트랜지스터를 갈랐다 : Planar -> Fin -> GAA

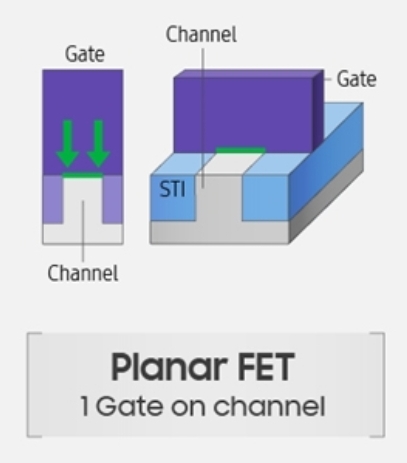

우선, FET의 개념부터 알고 갈게요. Field Effect Transistor의 약자로 트랜지스터가 얼마나 넓은 공간(Field)으로 효과(Effect)를 내는지를 얘기하는 거에요. 그래서 Planar FET, FinFET, GAAFET이라고들 하죠. Planar FET부터 볼게요. Planar는 '평면'을 뜻해요. 즉, 게이트(보라색)와 채널(회색)이 맞닿는 부분이 평면 한 부분인 것입니다. 트랜지스터의 기능은 하겠지만, 맞닿는 부분이 한 면 밖에 없어서 PPA라고 하는 전력, 성능, 면적이 부족해요. 참고로 PPA는 Power, Performance, Area를 뜻한답니다.

이번에는 FinFET구조를 봐볼게요. Fin은 물고기의 지느러미를 의미해요. 뾰족 튀어나와있는 지느러미를 생각하면 이해하기 쉬울겁니다. 기존 Planar FET에서는 채널 부분이 낮고 평평했죠. 하지만, FinFET은 지느러미가 뾰족 튀어나와있는 것 처럼 게이트를 뚫고 올라갑니다. 이 핀(Fin)이 위로 게이트를 뚫고 올라간다면, 접촉면이 3면이 됩니다. 양 옆을 게이트가 감싸주기 때문이죠. 획기적으로 접촉하는 면적이 커지고 게이트의 활용도가 더 커지다 보니 고성능을 요구하는 16나노부터 본격적으로 FinFET공정이 들어가게 됩니다. TSMC가 이를 정말 잘하고 있죠.

마지막으로 GAA(Gate-All-Around)입니다. 단어를 집중해서 봐보죠. 지금까지 Planar : Gate 1면 / Fin : Gate 3면 이었죠. 이제는 Gate가 All-Around입니다. 즉, 위,아래,오른쪽,왼쪽 모두 게이트가 채널을 감싸고 있는 형태가 된다는 것입니다. 그림을 보면 쉽게 이해가 가실거에요.

채널을 게이트가 감싸안으면서 4면 접촉이 가능하게 된거죠. 채널은 전류가 흐르는 곳이에요. 4면 전체가 다 흐르니 이제 전력량도 많아지고 여러개의 입구에서 전류가 흐르다 보니 효율성이 더 극대화 되겠죠. 즉, PPA가 이론적으로 올라갈 수 있다는 것입니다. 왜 이론적이란 말을 했냐면은 아직 성능 검증이 안됐기 때문이에요. 아래에서 자세히 설명 드릴게요.

정리

1. Planar FET, FinFET, GAA 구분은 채널 몇개의 면이 게이트와 접촉하는지에 따라 달렸다.

2. Planar 1개 / FinFET 3개 / GAA 4개

3. 채널 : 전류가 흐르는 곳 / Gate : 전류를 제어하는 곳

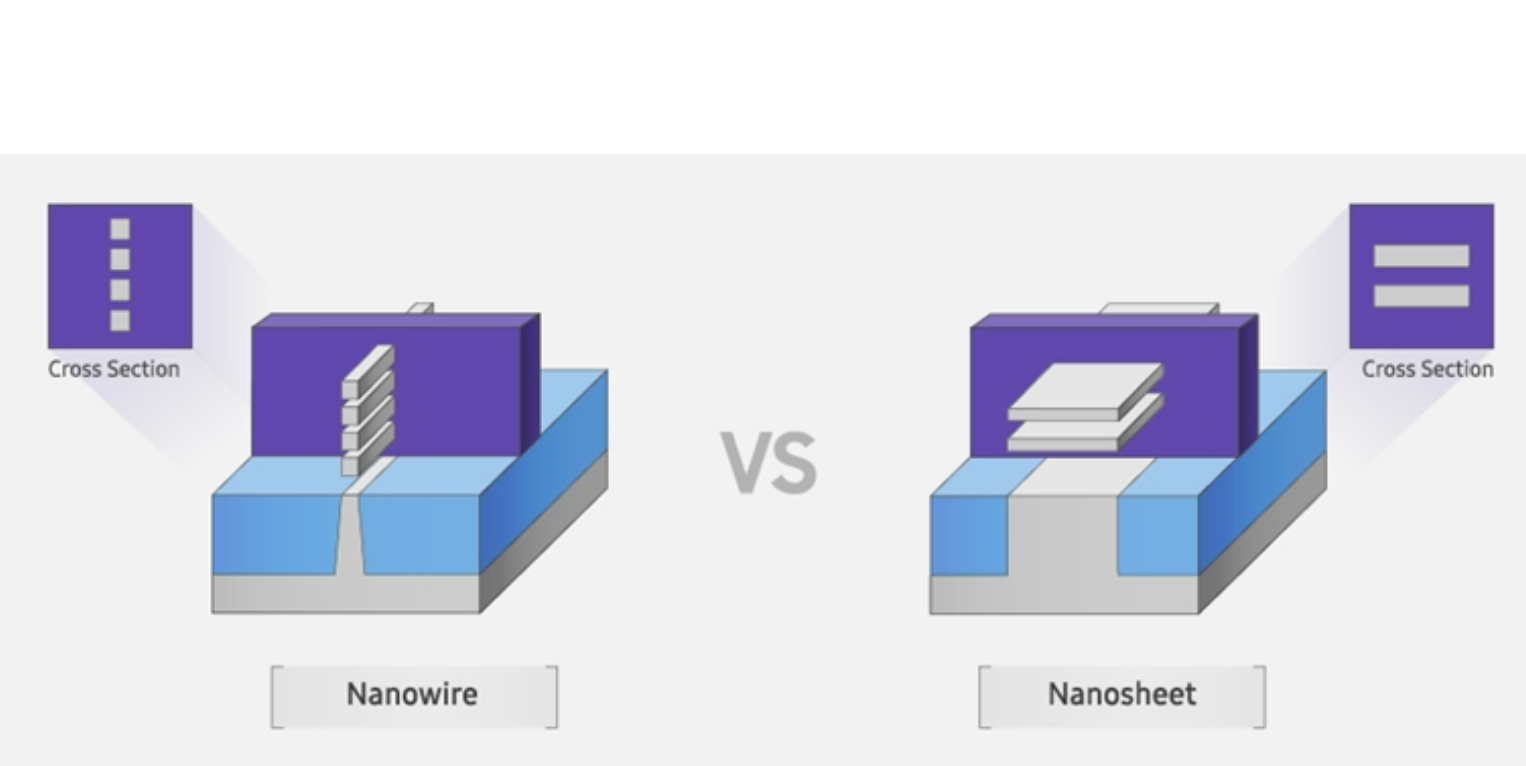

GAA Nanowire vs. GAA Nanosheet의 차이 : 채널과 게이트가 만나는 면적의 크기가 가른다

Wire하면 전 유선이어폰의 줄 부터 생각이 나요. 둥글고 얇은 줄이죠. 여기에 나노를 붙이면, 정말 둥글고 얇은 줄이 되는 것입니다. 둥글고 얇다 보니 핀의 면적이 넓지 못해서 게이트가 감싸는 면적이 적습니다. 한 마디로, 한개의 소자가 고성능을 내기에는 너무나 작은 것이죠. 전류가 적게 들어올테니깐요.

삼성전자는 Wire -> sheet로 바꿉니다. Sheet는 Wire보다 면적이 압도적으로 넓어집니다. 유선이어폰보다 책 한권이 훨씬 큰 것 처럼 말이죠. 이것을 Nanosheet라고 하는 것입니다.

TSMC는 왜 핀펫(FinFET)을 계속 고수 할까? : 사업은 기술로 하는게 아니야. 고객과 약속으로 하는거야.

TSMC는 앞으로 최소 2년여간은 차세대 각광받는 3나노에서도 핀펫구조로 간다고 이미 선언을 했죠. 대체, GAA가 PAA(Power, Performance, Area)면에서 모두 우수하다는데, 왜 TSMC는 핀펫구조로 간다고 할까요? 이는 고객과 약속한 정해진 시간, 비용, 효율을 지키기 위해서입닌다. 아니 무슨 돈 버는데 당위성 얘기를 하는지 궁금해하는 분들도 있겠죠. 사실, TSMC가 굉장히 영리한 것입니다. TSMC의 핀펫공정은 이미 저전력, 고성능, 적은 면적으로 소문이 나있죠. 그러니까, 파운드리 시장에서 점유율 50%이상을 차지하겠죠. 독점이죠.

TSMC가 보기에는 GAA공정은 핀의 아랫면까지 게이트가 맞닿야하니까 공정이 추가가 되고 이는 비용을 유발하죠. 또한, 아무리 핀이 게이트와 만나는 면이 3면 -> 4면으로 바뀌었다고 하더라도, 이론적으로만 PPA가 개선되는지는 실제로 양산을 해서 직접 보여준 것이 아니라는거죠. 이러한 상황에서 TSMC는 PPA의 불확실성과 이로 인한 고객과의 신뢰가 깨지는 것을 두려워하는 것 같아요. 사실, 파운드리업체와 펩리스업체는 쿠팡처럼 어제 주문해서 내일 새벽에 오는 그러한 것이 아닙니다. 최소 2~3년 간의 끊임없는 회의와 전략을 세우고 신뢰를 구축해야 나올 수 있는 제품인 것이죠. 이는 TSMC 사외이사로 마이크로소프트 CEO 사티아 나델라가 있는 이유가 괜한 것이 아니에요.

물론, GAA방식이 PPA 면에서 모두 우수한 성적을 보여준다면, TSMC는 다급해질 것입니다. 그렇기에 TSMC도 GAA 방식으로 나아가야한다는 것은 인지하고 있죠. 다만, 지금은 아니라는 거죠. GAA방식을 대비하는 차원에서 TSMC가 내놓은 것이 핀플렉스(FinFlex) 공정입니다. 핀펫구조에서 핀과 게이트의 맞닿는 면적을 늘리려면, 핀자체를 늘려야하죠. 이는 트랜지스터의 크기를 키우는 한계가 있습니다. 다만, TSMC는 맞닿는 3개의 면을 조금 더 길게 쭈욱 빼기로 하고 한 트랜지스터에 핀을 1개, 어쩔 때는 2~3개까지 유동적으로 만든다는 계획인 것 같습니다. 이는 고객이 원하는 제품에 모든 부분에서 고성능을 낼 필요는 없고 특정 기능을 할 때 PPA를 높이면 되기 때문에 그러한 부분에서는 핀을 더 늘려 성능을 더 내겠다는 것이죠. 말 그대로 Fin이 Flex해지는 것입니다.

정리

1. GAA방식이 삼성이 최초로 한 것은 맞지만, 그 성능입증은 아직 되지 않았다 -> 앞으로 누가 발주를 넣는지가 중요

2. GAA성능 검증이 안되어서, TSMC는 FinFET으로 앞으로 2년여간 더 하겠다고 선언.

3. GAA의 PPA 검증만 된다면 삼성이 크게 도약할 것으로 기대.

'국내주식 > News, Trading Note' 카테고리의 다른 글

| 태광산업이 흥국생명 유상증자참여 논란, 쉽게 설명드립니다. (ft. 석유화학제품 파는 기업이 보험사에 투자..? + RBC 설명) (1) | 2022.12.10 |

|---|---|

| 제로칼로리 음료수, 과연 믿고 마셔도 되는 걸까? (ft. 까다롭지만 정말 쉽게 설명드림) (0) | 2022.12.01 |

| LG화학이 고려아연주식을 2576억원이나 매수한 이유(ft. 정말 쉽고 간단하게 설명드림) (1) | 2022.11.23 |

| 월드컵 사우디 vs. 아르헨티나 경기에서 사우디여성 관객은 없는 이유? (ft. 놀라자빠지네..) (1) | 2022.11.22 |

| 버스정류장 의자가 갑자기 따뜻해진 이유는? (ft. 정말 간단하고 쉽게 설명드림! ) (0) | 2022.11.21 |